數字集成電路設計(二) Verilog HDL基礎知識與集成電路設計服務

數字集成電路設計是現代電子工程領域的核心技術之一,而Verilog HDL作為主流的硬件描述語言,在其中扮演著至關重要的角色。本文將從Verilog HDL的基礎知識入手,并探討集成電路設計服務的相關內容。

一、Verilog HDL基礎知識

Verilog HDL(硬件描述語言)是一種用于數字系統建模、設計和驗證的語言。它支持從系統級到門級的多層次抽象描述,能夠高效地描述數字電路的結構和行為。

1. 基本語法結構

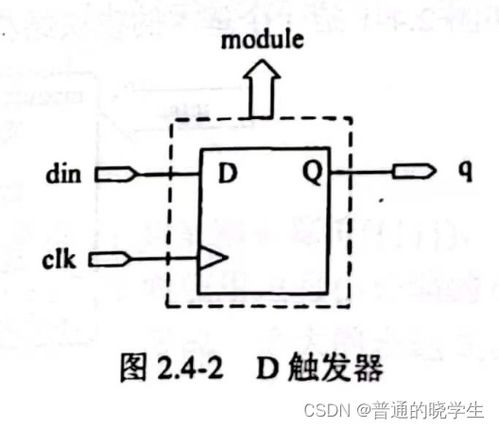

Verilog HDL包含模塊(module)、端口(port)、信號(wire/reg)等基本元素。模塊是Verilog設計的基本單元,通過端口與外部環境交互。信號分為線網類型(wire)和寄存器類型(reg),分別用于連接組合邏輯和存儲時序邏輯。

2. 數據類型與運算符

Verilog支持多種數據類型,包括標量(scalar)、向量(vector)和數組(array)。常用的運算符包括算術運算符、關系運算符、邏輯運算符和位運算符等,這些運算符的組合能夠描述復雜的數字邏輯功能。

3. 行為級建模

通過always塊和initial塊,Verilog可以描述電路的行為。always塊用于描述重復執行的邏輯,而initial塊僅在仿真開始時執行一次。這些結構使得設計者能夠以類似軟件編程的方式描述硬件行為。

4. 結構級建模

Verilog支持通過實例化已有模塊來構建更大的系統,這種層次化設計方法大大提高了代碼的可重用性和可維護性。

二、集成電路設計服務

隨著半導體技術的不斷發展,專業的集成電路設計服務變得越來越重要。這些服務涵蓋了從概念到成品的全過程,主要包括:

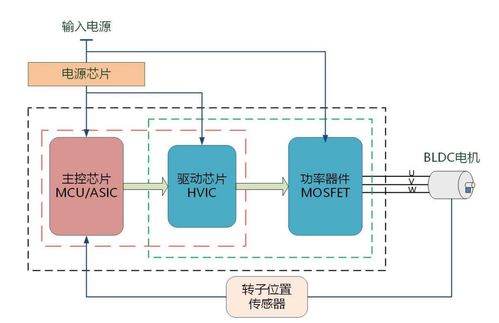

1. 架構設計

根據客戶需求,設計團隊會確定芯片的整體架構,包括功能模塊劃分、接口定義和性能指標等。

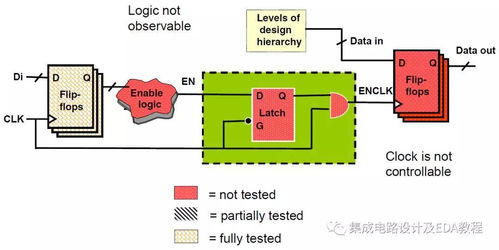

2. RTL設計與驗證

使用Verilog等硬件描述語言進行寄存器傳輸級(RTL)設計,并通過仿真驗證其功能正確性。這一階段通常需要編寫大量的測試用例,確保設計滿足規格要求。

3. 邏輯綜合與時序分析

將RTL代碼轉換為門級網表,并進行時序分析以確保電路能夠在目標頻率下穩定工作。

4. 物理設計

包括布局規劃、布線、時鐘樹綜合等步驟,將邏輯設計轉換為實際的物理版圖。

5. 測試與封裝

設計完成后,需要進行芯片測試和封裝,確保最終產品符合質量和可靠性要求。

專業的集成電路設計服務提供商通常擁有豐富的項目經驗和先進的設計工具,能夠為客戶提供從概念到量產的全流程解決方案。隨著AI、物聯網等新興技術的發展,對高性能、低功耗數字集成電路的需求日益增長,Verilog HDL和專業的IC設計服務將繼續在推動技術進步方面發揮關鍵作用。

如若轉載,請注明出處:http://m.cuobeng.cn/product/38.html

更新時間:2026-03-01 23:34:20